MECHATROLINK-III Master/Slave IP

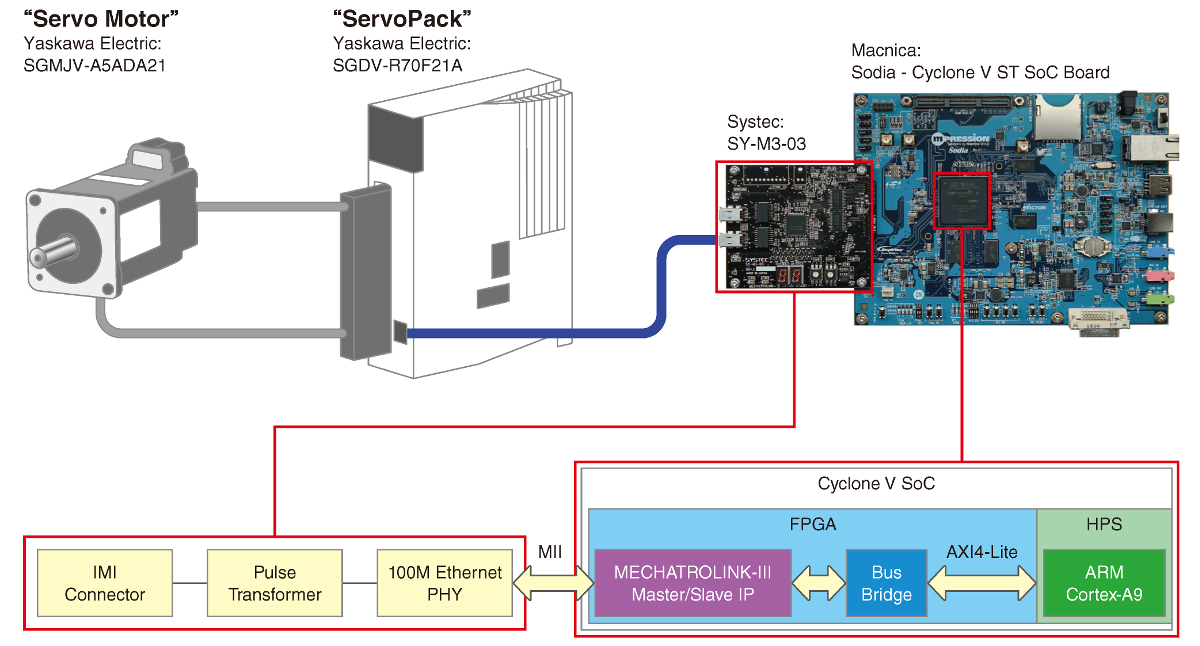

Compatible with Yaskawa Electric JL-100/JL-102 LSI

MECHATROLINK-III Master/Slave IP together with CPU communicates with the products adapting

MECHATROLINK-III standardized by MECHATROLINK Members Association.

Features

- Functionally compatible with JL-100 which is the ASIC for MECHATROLINK-III Master/Slave communication.

- Parameters required for MECHATROLINK-III communication are set either by cpu or through external pins.

- Certified by MECHATROLINK Members Association.

Supported Devices

- Cyclone V

-

Texas Instruments Sitara™ (Single Slave)

* Please contact Macnica sales department about other devices.

Deliverables

- IP (Encrypted netlist)

- Reference design

- User’s manual

Device Resource Utilization

| Items | Master IP | Slave IP | Multi-Slave IP |

|---|---|---|---|

| ALMs | 8,468 | 8,525 | 8,468 |

| Total block memory bits | 459,776 | 459,776 | 459,776 |

| RAM Blocks | 62 | 62 | 62 |

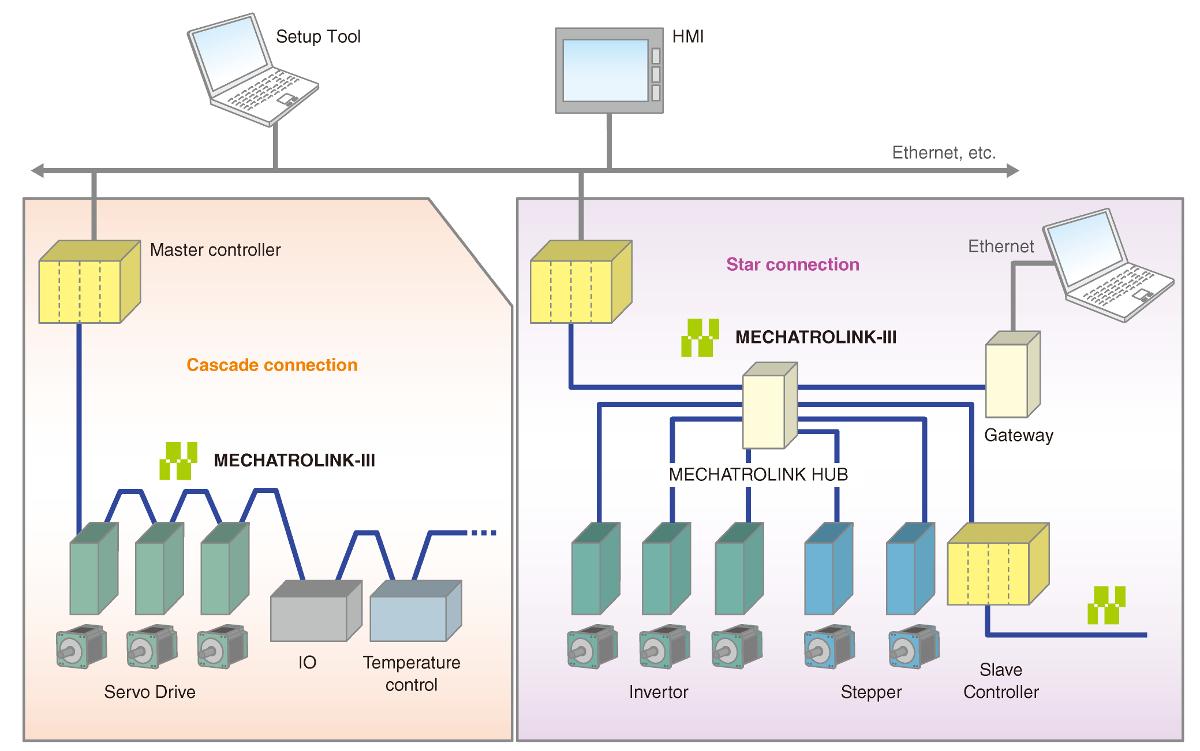

System Configuration Example

Evaluation Demo

- Link to Sodia Board

Downloads