SLVS-EC Rx IP

Next generation CMOS image sensor interface

SLVS-EC is the next-generation, high-speed interface for high-resolution CMOS image sensors.

This standard is tolerant of lane-to-lane skew because of embedded clock technology that simplifies board-level design of high-speed and long-distance data transmission.

Originally developed and licensed by Sony, SLVS-EC is now starting to be supported by multiple image sensor suppliers.

IP Core Features

- Compliant with SLVS-EC Specification v1.2 and v2.0 by Sony

- Supports various functions defined by the SLVS-EC Link layer (FPGA dPCS/PMA is used as Physical layer)

- Supports Byte-to-Pixel conversion for various lane-configurations

- Supports Header analysis and Payload error detection

Specifications

| Feature | Description |

|---|---|

| Number of Lanes | 1, 2, 4, 6, 8 |

| Baud Grade |

1 (1.152 to 1.25 Gbps) 2 (2.304 to 2.5 Gbps) 3 (4.608 to 5.0 Gbps - supported in v2.0) |

| Bit per Pixel | 8, 10, 12, 14, 16 |

| CRC | Limited* |

| ECC | Supported |

| Embedded Data | Supported |

| Dynamic Mode Change | Supported |

| Multiple Stream | If needed |

* The operating frequency may not be achievable depending on the speed grade, numberof lanes, and other factors of the FPGA used. Please contact Macnica sales department for information about limitations.

Supported Devices

- Intel Cyclone V GX/SX (v1.2)

- Intel Cyclone 10 GX (v1.2 / 2.0)

- Intel Arria 10 GX/SX (v1.2 / 2.0)

- Xilinx Artix 7 (v1.2)

- Xilinx Kintex 7 (v1.2 / 2.0)

- Xilinx Kintex Ultrascale (v1.2 /2.0)

- Xilinx Kintex Ultrascale (v1.2 / 2.0)

* Please contact your local Macnica sales representative or through contact form for information about other devices.

Deliverable

- Encrypted RTL (Verilog HDL)

- Reference design

- Simulation environment (For ModelSim)

- User's manual, Reference manual

Device Resource Utilization

Resource Utilization in case of 8 LANE Full Configuration

| Items | Cyclone® V GX | Arria® 10 GX | ||

| w/o ECC | w/ECC | w/o ECC | w/ECC | |

| ALMs | 4711 | 8242 | 3930 | 7555 |

| Total Registers | 4328 | 6664 | 3778 | 6079 |

| Total block memory bits | 4096 | 13312 | 2560 | 11776 |

* The above values are estimated resource utilization of the IP and Transceivers; they may vary depending on your system configuration.

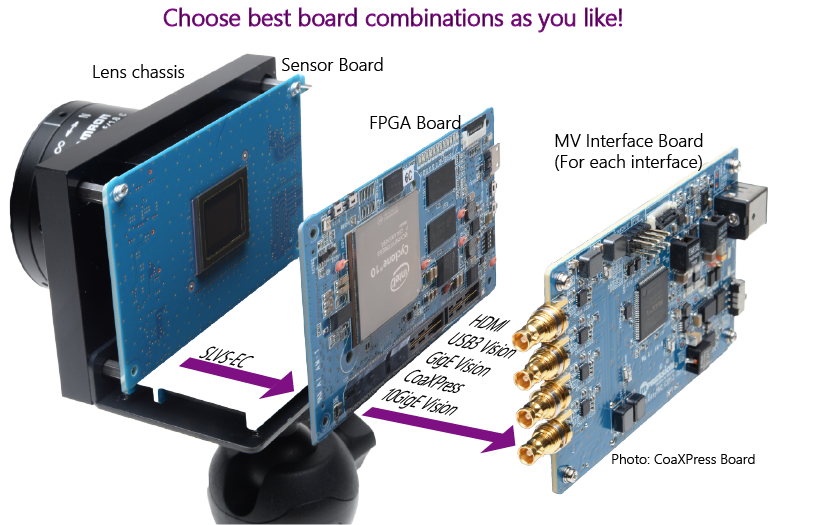

Evaluation/Development Environment

Macnica EasyMVC is the evaluation and development environment for SLVS-EC IP core, providing the whole infrastructure needed, including a variety of image sensor boards with Sony IMX image sensors with SLVS-C interface, FPGA boards with supported FPGAs, and interface boards to support various machine vision interface standards.